05 - Input/Output

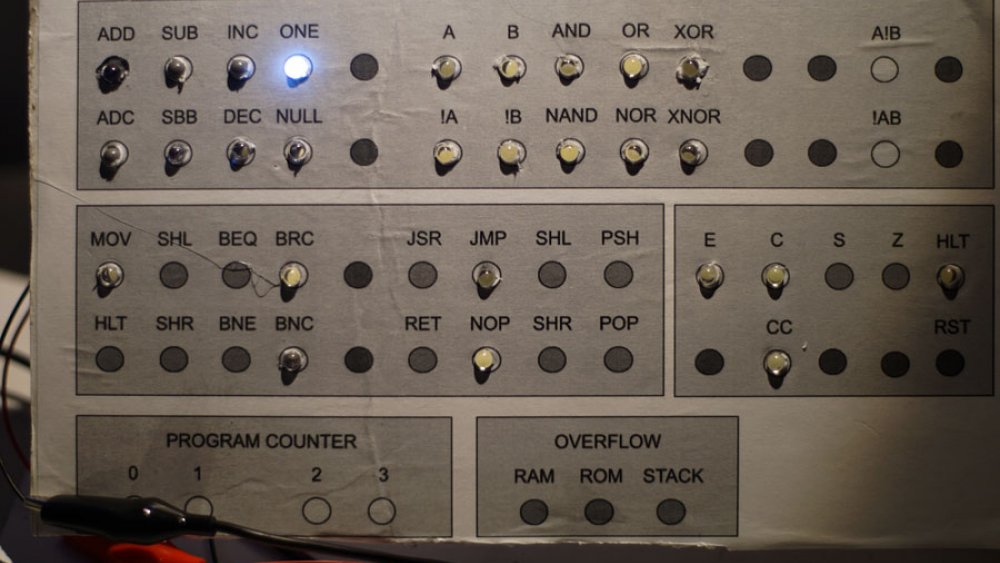

Front Panel Instruction Indicators - Cardboard Prototype

It is pretty rough, but this cardboard prototype of the "Instruction Indicators" panel will be pretty useful when I am working on control logic. I am working on the computer instructions / operations, and this will greatly speed development and allow easy confirmation that the control signals are correct.

Making a prototype was also helpful to identify some issues with the current design, including how impossibly bright the LEDs are. The illuminated LED in the above photo has two layers of opaque plastic covering it. I will be experimenting with dips and coating in the coming weeks, but the best option may be to power the LEDS from a separate 3-volt system to improve the lifespan of the LEDs.

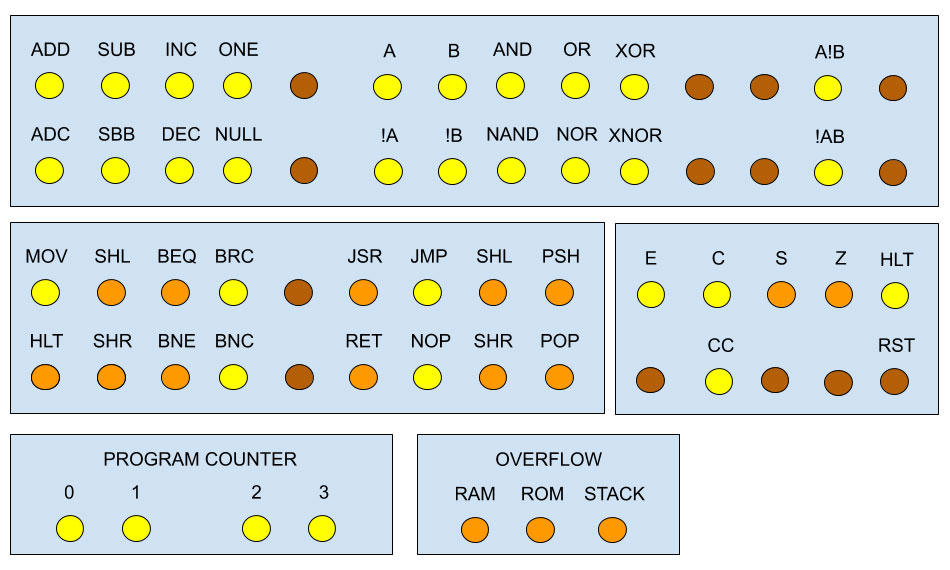

Instructions and Indicator LEDS

I will go over the actual operations and flags in detail, in future posts. For now, I just want to talk briefly about the blocks as currently envisioned. Before I do, there are three colours of LEDs in the graphic, as follows:

Yellow - Planned to be implemented in the first phase.

Orange - Planned to be implemented in the second phase.

Brown - Set aside for future use.

ALU Block

The ALU takes a 5-bit control word and does not require any additional control or decoding logic, so it is trivial to implement ALU functionality. This block is basically broken into three sections:

Left - Arithmetic... A plus B

Centre - Logic A XOR B

Right - Complex Logic A AND NOT B

Command Block

This block contains indicators for non-ALU operations, and includes things like register copy, jumps, branches, and stack related functions

Flags Block

This block, to the right of the Command Block, displays the flag indicators. The carry flag can be cleared, and thus there is a separate indicator for that. Indicators for system halt and reset round this block out.

Program Counter Block

This block contains the four dedicated counters assigned for RAM and ROM addressing, in two pairs. Normally only one counter will be active at a time.

Overflow Block

This block contains three indicators that will be illuminated when RAM addressing overflows, when ROM addressing overflows, and when the Stack Pointer overflows. Note that an overflow error will be thrown for an "under flow" as well; any time an address counter rolls over or resets an error will be thrown.

Card Pans - Block Diagrams

I expect there will be several counters, optimally two for RAM, two for ROM, and one for the Stack. If we include a separate "Return Address Stack", that will require a counter to drive the address as well.

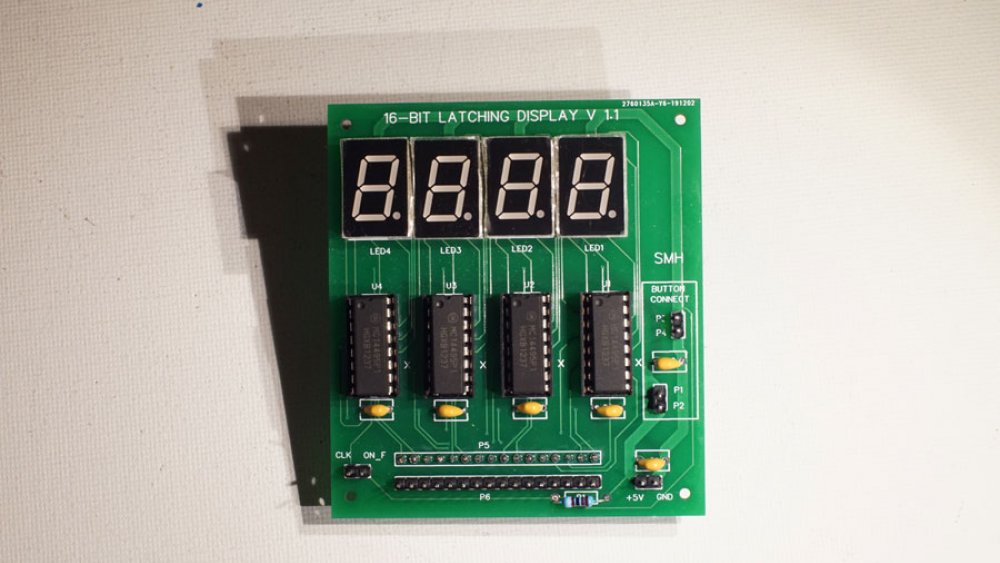

16-bit Hex Display Board

I have wanted a decent display system since I started this hobby in 2015, and finally had the opportunity to create something. The front-panel that I have planned will display binary output for the (control, signal, data, and address) buses, but will have four-digit hex displays for registers. The reason for this is it is much easier to quickly see values when they are displayed in hexadecimal, but binary is obviously better for showing which bits are set.

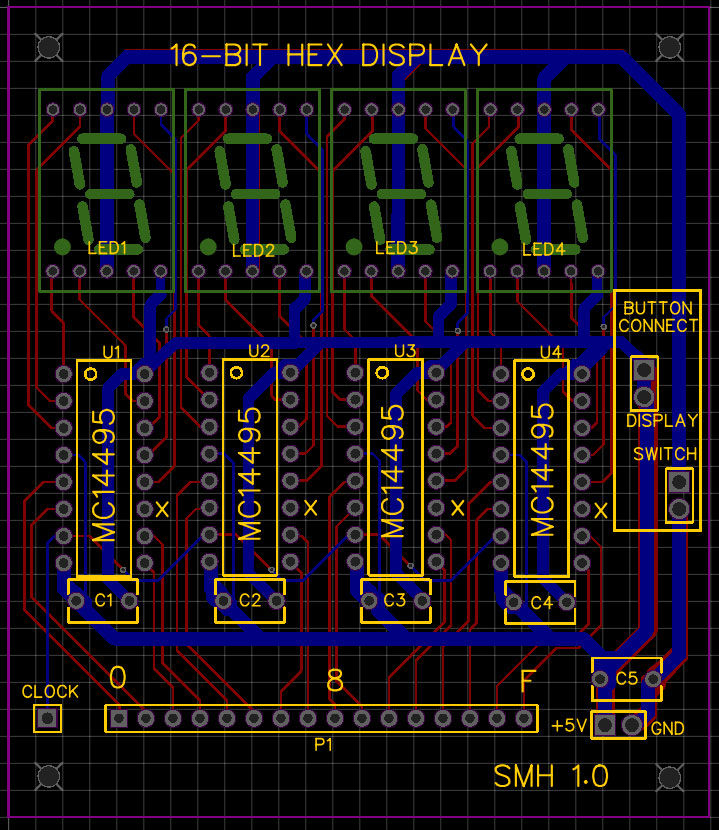

This display board was designed in EasyEDA, directly as a PCB... so no schematic. I probably should have created a schematic first, but I am a prototyper at heart and it feels better to me to lay out PCBs the way I lay out breadboards. I never draw circuits before breadboarding, so I am trying to do the same with these PCBs.

This is not the final version, but it is close and I wanted to compare it to the final version I had made. Because I do not do schematics, I end up laying out the PCB several times as I refine the components and positioning. This board is relatively simple, as it just needs four MC14995s to drive four 7-segment common cathode displays. I added a 16-pin header to connect the board, a clock pin, and power. Because I plan to use these with a front panel, there are pins to connect to controls... but for stand-alone use the switch pins can be shorted or jumpered. The decoupling capacitors are optional.

So, what was wrong with this design? Several things. First, I had planned to mount the displays on the reverse side, but I became confused during the layout and did not lay the traces 100% correctly. A second issue was the 16-pin header... really, I needed two so that the display could act as a pass-through.

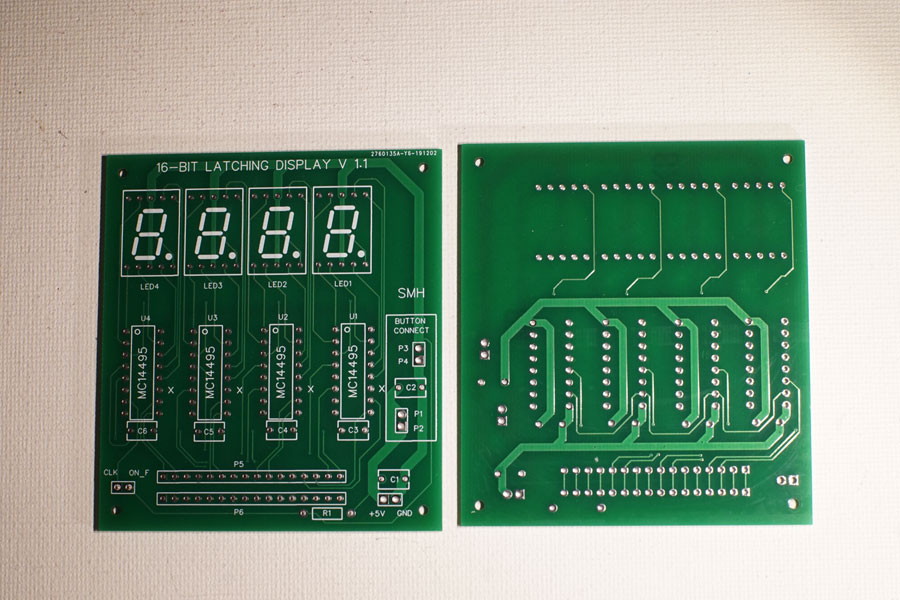

The final version is very similar to the 1.0 version, with the most notable exceptions being the displays and an extra 16-pin header. Front-panel related pin headers have been adjusted as well. The R1 resistor on the bottom of the board is a pull-up for the "on flag" pin.

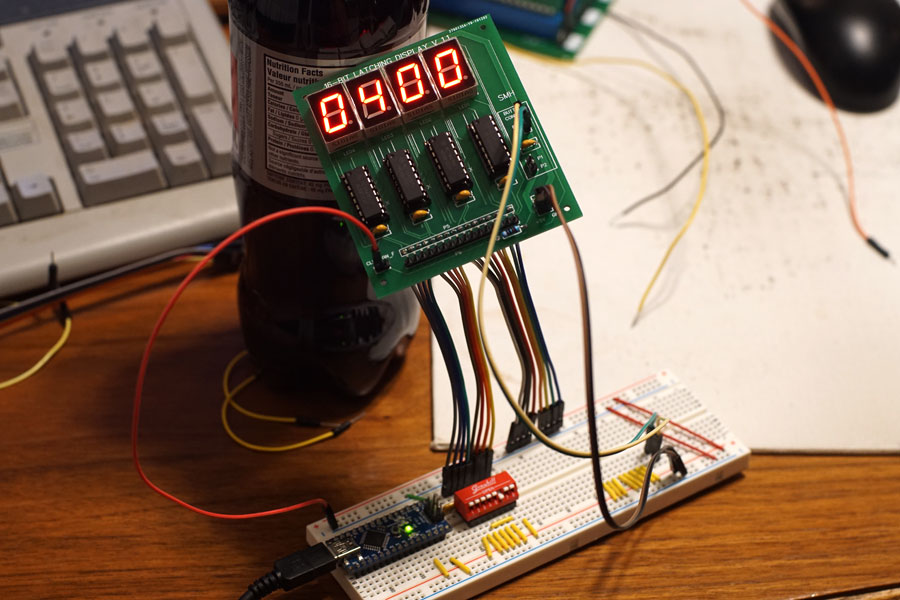

Fully populated, the hex display board was tested with a breadboard, 8-bits at a time (I only had one dip switch unit handy).

I have enough PCBs to build ten display boards, but I probably only need five or six, maybe a couple more for other projects.